# The BOA Methodology

#### **Presentation to SNUG `97**

### Wilson Snyder

Digital Semiconductor

### Agenda

What is Boa? Goals & Overview Timing File Re-Constraining Synthesis script format Parallel compilation Suggestions to Synopsys Conclusions & Credits

### What is Boa?

A constraint-driven compile methodology

• Begins with manual time-budgeting, then improves

### Estimated to half cycle time

- Compared to top-down or bottom-up techniques

- Used on core logic chips:

- Kodiak P 50K Gates 66 MHz

- Kodiak C 60K Gates 66 MHz

- 21271-C\* 180K Gates 83++ MHz

- 21271-D\* 120K Gates 83++ MHz

- 21271-P\* 120K Gates 83++ MHz

### \*Marketing Plug

- Chipset for the 21264, the fastest microprocessor.

- Presented at Microprocessor Forum, Oct `96.

### What were Boa's goals?

### Best cycle time

• Hand generated time budgets do well but take effort

### Eliminate redundant information

- set\_input\_delay on signal destination modules

- set\_output\_delay on signal source module

- set\_fake\_path in Synopsys, Timing Analyzer, ...

- Allow stand-alone block compiles

- Without creating special scripts

- Enable structural instantiations

- Hide internal details where possible

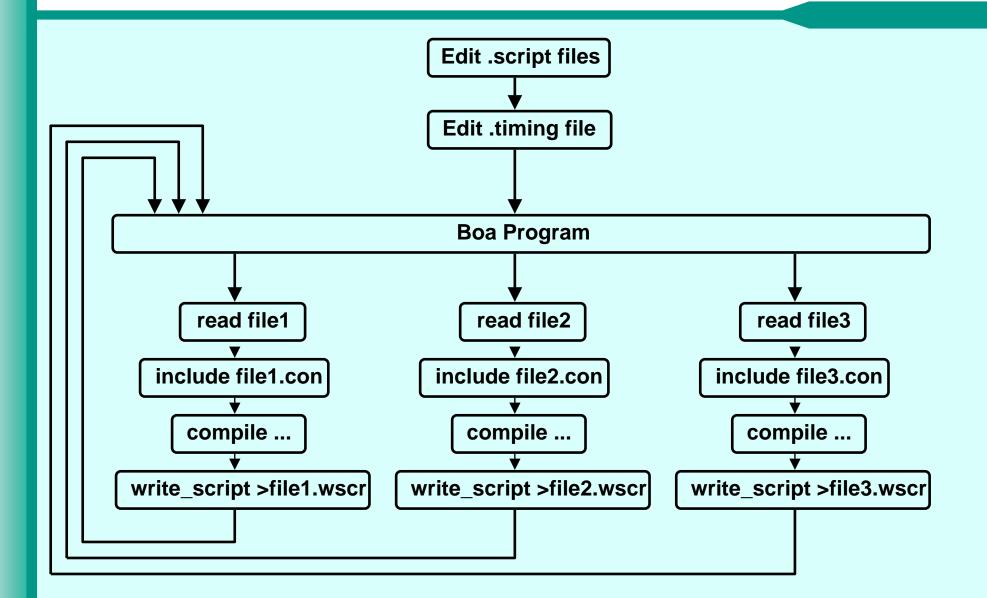

### **Boa Methodology Flow**

# **Boa Timing File**

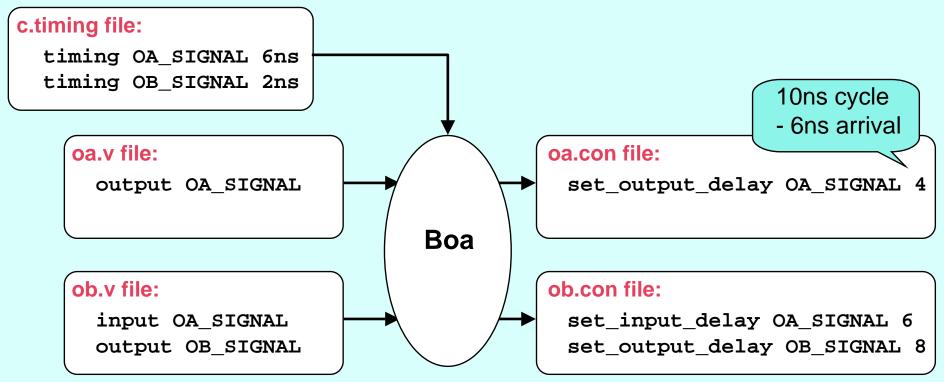

All port constraints are stored by signal in a single file

Users create the .timing file, and keep it up-to-date.

Boa reads the .timing file, and creates .con constraint files for every Verilog module.

## **Boa Timing File Commands (1 of 2)**

### timing {signal} {time}

- Places set\_input\_delay on ports that input the signal.

- Places set\_output\_delay on ports that output the signal.

- Delay times are recalculated by Boa after the first loop

- weight {signal} {weight}

- Places group\_path on a single port.

- Weights may be recalculated by Boa.

# **Boa Timing File Commands (2 of 2)**

#### Ioading {signal} /wire /port

- Places set\_load Of set\_wire\_load in constraints.

- If omitted for any signal, has reasonable default.

- (Synopsys defaults to zero loading! Definitely optimistic!)

### driving {signal} {cell}

- Places set\_driving\_cell in constraints.

- If omitted for any signal, has reasonable default.

### path {signal}

- Places set\_false\_path in constraints.

- Passed on to downstream static timing analyzers.

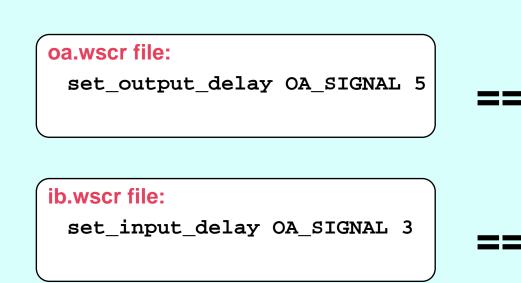

### **Timing Feedback via Write\_script**

To correct timing file errors, we want feedback of actual timing numbers.

- Could use a static timing analyzer or report\_timing.

- Characterize and write\_script do the same thing!

Make a .wscr write\_script output for every module.

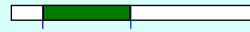

The soonest destination of the signal needs the input before (cycle\_time-5ns).

The latest source of the signal generates the output 3ns after the clock edge.

## **Boa Re-Constraining (1 of 2)**

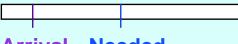

#### Slack Paths

Take arrival and needed times

Arrival Needed

#### Calculate slack

Scale slack by source logic %age

#### Add scaled slack

## **Boa Re-Constraining (2 of 2)**

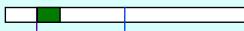

#### **Slack Paths Breaking Paths** Take arrival and needed times Take arrival and needed times **Needed Arrival Arrival Needed** Calculate slack Calculate effective cycle time Scale slack by source logic % age Find midpoint of needed & arrival Add scaled slack Scale midpoint to make cycle time Updated Updated Create weight (group path)

Weight = 1 + 6 \* (violation/cycle time)

### **Boa Annotation**

#### Show signal with timing in source code:

- 3.0 (Gray) Original time user entered in .timing file

- 6.1 (Yellow) Updated time calculated by Boa

- **4.6** (Purple) Arrival time, from source logic delay

- **8.1** (Blue) Needed time, from destination logic delay

- 3.2 (Green) Slack (Needed-Arrival)

- -1.3 (Red) Violation Slack (Needed-Arrival)

#### How it works:

Using GNU Emacs 19: Read the source file Search and replace SIG with SIG`3.0...' Create overlays for each highlight color

# **Boa Parallel Compiling**

- With each block being compiled separately, we can compile each block on a different machine!

- Split script commands into tasks, indivisible blocks of commands that must execute together.

- task { echo "Do this on some machine."}

- primary\_task { echo "Do this on machine #1."}

- non\_primary\_task { echo "Do this on machines #2...n."}

- If tasks need to be completed in order, add a sync.

- task { echo "Finish this task."}

- task { echo "And this task"}

- sync

- echo "Before printing this."

- Parallelization gives > 3 times the throughput when using 4 machines!

- Code included on Synopsys SNUG website.

### **Synopsys Improvements**

- Use multiprocessors and network computes Associative arrays (like Perl) Add a "need\_compile" attribute, is\_mapped breaks Reset on behavioral code Set on a compile OR structural code Compile -so\_high\_that\_youll\_try\_everything Roughly: compile -map\_effort high (2 times) compile -map\_effort high -incremental (2x) Disable echoing mode foo = "x" >/dev/null Latch timing is broken

- Can't analyze both D->Q flow-through and D->clock paths

### Credits

Much thanks to the co-developers of Boa:

Paul Wasson, who did much of the Boa program, named Boa, and got me into Perl!

Steve Kolecki, who provided ideas, and adapted the methodology to the 21271

For the full paper, search for Boa using SOLV-IT!

Please remember to fill out the feedback forms!